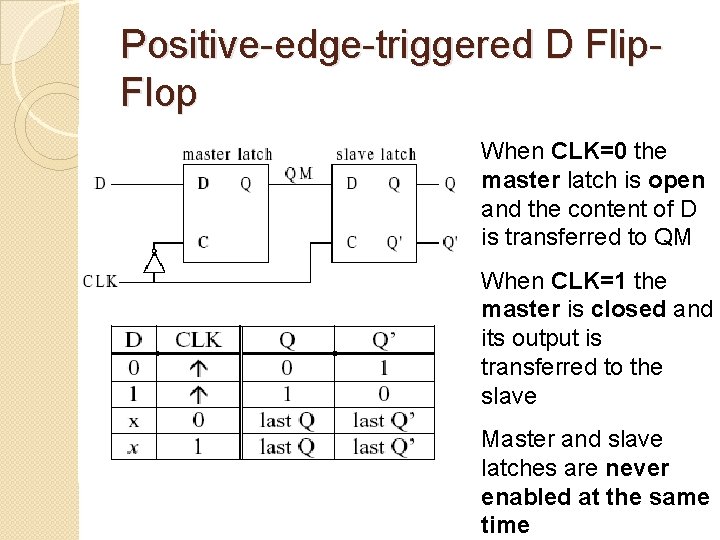

Notice that although the clock inputs on the circuit symbols suggest that this is a negative edge triggered device, data is actually taken into FF1 on the POSITIVE going edge of the CK pulse. Circuit symbols for the master-slave device are very similar to those for edgetriggered flip-flops, but are now divided into two sections by a dotted line, as also illustrated in Fig 5.3.6.įF1 (the master flip-flop) is a positive edge triggered device, and an inverted version of the CK pulse is fed from the main CK input to FF2 (the slave), also positive edge triggered. 5.3.6 where two D type flip-flops are incorporated in a single device, this is the D type master-slave flip-flop. Yet a further version of the D Type flip-flop is shown in Fig. 5.3.6 The D Type Master Slave Flip-flop The D Type Master Slave Flip-Flop At the positive going edge of pulse j, input D regains control, but as D is high and Q is already high, no change in output Q occurs.įinally, just before pulse k, the asynchronous reset input ( R) goes low and resets Q to its low level (logic 0), which again causes the D input to be ignored.įig. The flip-flop then ignores pulse d while S is low, but as S returns high, and D has also returned to its high state before pulse e, Q remains high during pulse e.Īt the positive going edge of pulse h, the low level of input D remains, keeping Q low, but between pulses h and i, the S input goes low, overriding any action of D and immediately making Q high.ĭ is still high at the positive going edge of pulse f, and because the flip-flop is positive edge triggered, the change in the logic level of D during pulse f is ignored until the positive going edge of pulse g, which resets Q to its low level.Ĭlock pulse i is again ignored, due to S being in its active low state and Q remains high, under the control of S until just before pulse j. Just before pulse c the D input goes low, so at the positive going edge of pulse c, Q goes low.īetween pulses c and d the asynchronous S input goes low and immediately sets Q high. 5.3.5.Īt the positive going edges of clock pulses a and b, the D input is high so Q is also high. A timing diagram illustrating the action of a positive edge triggered device is shown in Fig. The ‘Edge triggered D type flip-flop with asynchronous preset and clear capability’, although developed from the basic SR flip-flop becomes a very versatile flip-flop with many uses. 5.3.5 Typical Schematic Symbols for D Type Edge Triggered Flip-Flops The name Data Latch refers to a D Type flip-flop that is level triggered, as the data (1 or 0) appearing at D can be held or ‘latched’ at any time whilst the CK input is at a high level (logic 1).Īs can be seen from the timing diagram shown in Fig 5.3.2, if the data at D changes during this time, the Q output assumes the same logic level as the D.įig. If D = 0 then R must be 1 and S must be 0, causing Q to be reset to 0. 5.3.1, if D = 1, then S must be 1 and R must be 0, therefore Q is SET to 1. Provided that the CK input is high (at logic 1), then whichever logic state is at D will appear at output Q and (unlike the SR flip-flops) Q is always the inverse of Q).

5.3.1 is called a level triggered D Type flip-flop because whether the D input is active or not depends on the logic level of the clock input. 5.3.1 shows this as a ‘don’t care’ state (X). Operation.Īs long as the clock input is low, changes at the D input make no difference to the outputs. The S and R inputs are now replaced by a single D input, and all D type flip-flops have a clock input. This simple modification prevents both the indeterminate and non-allowed states of the SR flip-flop. The simplest form of D Type flip-flop is basically a high activated SR type with an additional inverter to ensure that the S and R inputs cannot both be high or both low at the same time. To avoid the ambiguity in the title therefore, it is usually known simply as the D Type. 5.3.1 together with its truth table and a typical schematic circuit symbol, may be called a Data flip-flop because of its ability to ‘latch’ and remember data, or a Delay flip-flop because latching and remembering data can be used to create a delay in the progress of that data through a circuit.

its indeterminate output and non-allowed logic states) described in Digital Electronics Module 5.2 is overcome by the D type flip-flop. The major drawback of the SR flip-flop (i.e.

0 kommentar(er)

0 kommentar(er)